Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

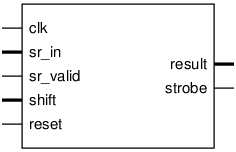

ccfilt

Description

Cascaded Differentiator and post-filter

also includes a barrel shifter to adjust scale to compensate

for changing decimation intervals

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

dw |

? |

? |

32 |

data width of mon_chan output: |

outw |

? |

? |

20 |

output data width |

shift_wi |

? |

? |

4 |

|

shift_base |

? |

? |

0 |

|

dsr_len |

? |

? |

12 |

expected length of strobe pattern |

use_hb |

? |

? |

1 |

compile-time conditional half-band code |

use_delay |

? |

? |

0 |

match pipeline length with use_hb case |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

sr_in[dw-1:0] |

Input |

|

sr_valid |

Input |

|

shift[shift_wi-1:0] |

Input |

controls scaling of result |

result[outw-1:0] |

Output |

|

reset |

Input |

|

strobe |

Output |

Implementation and use

The portable Verilog implementation can be found in ccfilt Source File