Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

phasex

Description

DMTD-inspired investigation into clock phasing

No on-chip analysis, but that could be added later once we see the captured patterns

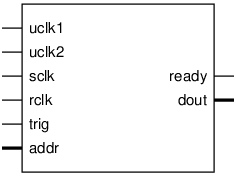

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

aw |

? |

? |

10 |

Ports

Signal |

Direction |

Description |

|---|---|---|

uclk1 |

Input |

unknown clock 1 |

uclk2 |

Input |

unknown clock 2 |

sclk |

Input |

sampling clock |

rclk |

Input |

readout clock (data transfer, local bus) |

trig |

Input |

|

ready |

Output |

|

addr[aw-1:0] |

Input |

|

dout[15:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in phasex Source File