Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

iq_deinterleaver

Description

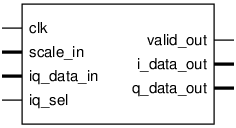

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

scale_wi |

? |

? |

18 |

Width of scale input and downscale factor |

dwi |

? |

? |

16 |

Width of iq stream |

davr |

? |

? |

4 |

Guard bits to keep at output of scale multiplication |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

scale_in[scale_wi-1:0] |

Input |

Scaling factor; scale is typically positive; |

iq_data_in[dwi-1:0] |

Input |

IQ interleaved data |

iq_sel |

Input |

1 (I), 0 (Q) |

valid_out |

Output |

|

i_data_out[dwi+davr-1:0] |

Output |

|

q_data_out[dwi+davr-1:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in iq_deinterleaver Source File

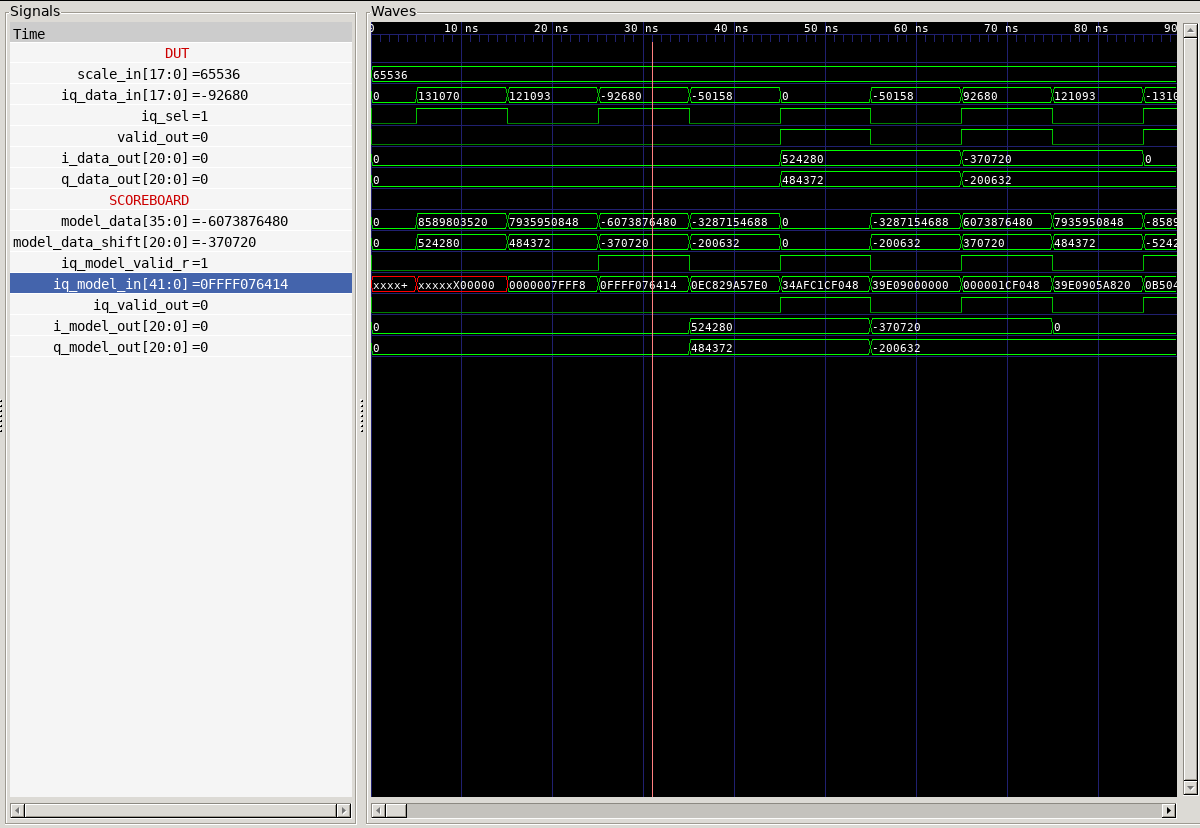

Timing Diagram

A GTKWave-generated timing diagram is shown below: