Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

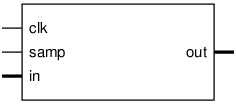

iq_inter

Description

Second-order CIC interpolation of an IQ data stream

Expect input valid for 2 cycles (marked by active-high samp signal)

out of 2*N.

Well, this is only the integration half of the CIC filter, someone

else (e.g., iq_intrp4) needs to do the differentiation.

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

dwi |

? |

? |

22 |

data width in |

dwo |

? |

? |

18 |

data width out |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

timespec 8.4 ns |

samp |

Input |

|

in[dwi-1:0] |

Input |

|

out[dwo-1:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in iq_inter Source File