Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

freq_count

Description

Synthesizes to 86 slices at 312 MHz in XC3Sxxx-4 using XST-8.2i

(well, that’s just the unknown frequency input; max sysclk is 132 MHz)

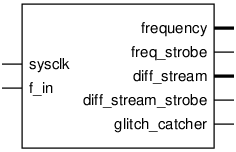

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

glitch_thresh |

? |

? |

2 |

|

refcnt_width |

? |

? |

24 |

|

freq_width |

? |

? |

28 |

|

initv |

? |

? |

0 |

Ports

Signal |

Direction |

Description |

|---|---|---|

sysclk |

Input |

timespec 8.0 ns |

f_in |

Input |

unknown input |

frequency[freq_width-1:0] |

Output |

|

freq_strobe |

Output |

|

diff_stream[15:0] |

Output |

stream of last 4 4-bit counts of f_in |

diff_stream_strobe |

Output |

strobe at f_sysclk/4 |

glitch_catcher |

Output |

Implementation and use

The portable Verilog implementation can be found in freq_count Source File

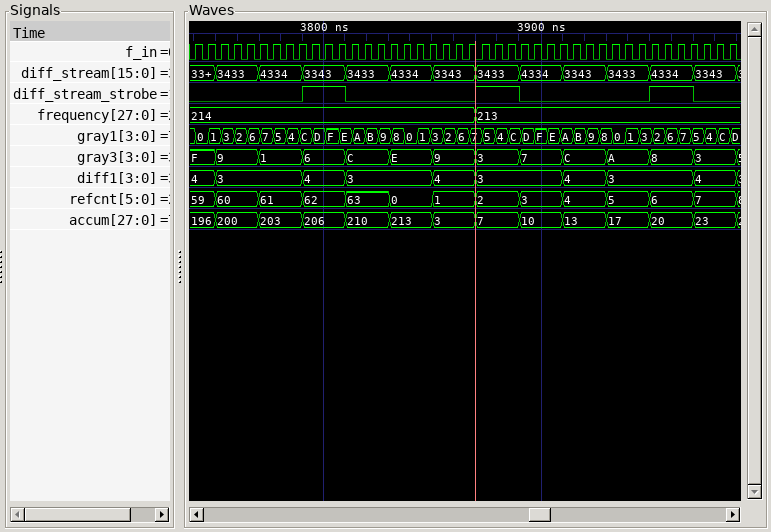

Timing Diagram

A GTKWave-generated timing diagram is shown below: