Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

afterburner

Description

Synthesizes to 47 slices and 1 MULT18X18 at 166 MHz in XC3Sxxx-4 using XST-9.2.04i

Use parameter triple instead of preprocessor variable AFTERBURNER_TRIPLE

User port coeff instead of parameter coeff

If the port coeff is set to a constant value, should synthesize identically

There is a latency of 3 clock cycles (??)

Note: The output of the module is Offset Binary

[It is perhaps stupid to have that here and it should be moved into another module]

CONCEPT: The mid point along the circle of a of 2 complex numbers that already lie

on a circle is not a plain average. To obtain the (real/imaginary) component

of this mid-point one has to multiply by what is called “coeff”

k = 0.5*sec(theta) .. where theta is the angle between the complex numbers

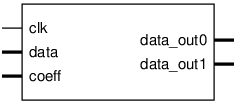

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

triple |

? |

? |

0 |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

timespec 6.0 ns |

data[16:0] |

Input |

This is level set data [.. a_n1, a_n2 ..] |

coeff[15:0] |

Input |

Coefficient to correct for interpolation |

data_out0[15:0] |

Output |

Interpolated [coeff*[..(a_n1+a_n2), (a_n2+a_n3),..]] |

data_out1[15:0] |

Output |

Untouched [.. a_n1, a_n2 ..] |

Implementation and use

The portable Verilog implementation can be found in afterburner Source File

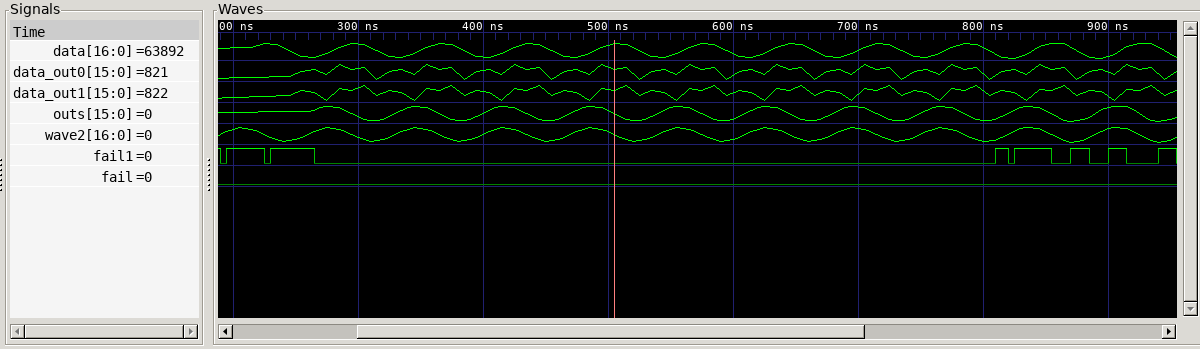

Timing Diagram

A GTKWave-generated timing diagram is shown below: