Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

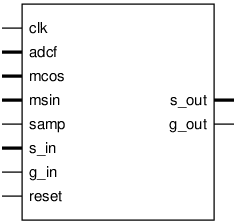

mon_2chan

Description

2 x 3-in-1 functionality

1. Mix an ADC output with LO sin (or) cos (see mixer.v)

2. Double CIC integrate the output signal from step-1. (via double_inte.v)

3. Take a sample from step-2 when the input samp is high AND

put the sampled data out on the stream when g_in is high (via serialize.v)

TODO: Find a better name

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

dwi |

? |

? |

16 |

data width |

rwi |

? |

? |

28 |

result width |

davr |

? |

? |

3 |

how many guard bits to keep in output of multiplier |

dwlo |

? |

? |

18 |

Local Oscillator data width |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

timespec 8.4 ns |

adcf[dwi-1:0] |

Input |

Full scale (?) ADC data, possibly muxed |

mcos[dwlo-1:0] |

Input |

|

msin[dwlo-1:0] |

Input |

|

samp |

Input |

mixer + double_integrated output capture trigger |

s_in[rwi-1:0] |

Input |

Stream IN |

s_out[rwi-1:0] |

Output |

Stream OUT |

g_in |

Input |

|

g_out |

Output |

|

reset |

Input |

Implementation and use

The portable Verilog implementation can be found in mon_2chan Source File