Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

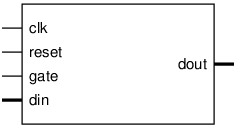

reg_delay

Description

Encapsulation of a register delay, z^{-n} in DSP-speak

Properly handles odd-ball special cases like len==0

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

dw |

? |

? |

16 |

Width of data |

len |

? |

? |

4 |

Cycles to delay |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

Rising edge clock input; all logic is synchronous in this domain |

reset |

Input |

Please tie to 0 if you can; see below |

gate |

Input |

Enable processing |

din[dw-1:0] |

Input |

Input data |

dout[dw-1:0] |

Output |

Output data |

Implementation and use

The portable Verilog implementation can be found in reg_delay Source File