Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

evr_ts_cdc

Description

Move tinyEVR’s 64-bit timestamp to another clock domain

Uses Gray codes to get (almost) ideal results.

Time delay is one evr_clk plus one-to-two usr_clk cycles.

Yes, that’s the inevitable clock-domain-crossing jitter.

The Gray code scheme fails at the time when ts_tcks gets reset to zero by the evr_pps event.

As a workaround, the first _two_ values of the output usr_tcks are forced to zero, every time usr_secs is updated.

Obligatory xkcd: https://xkcd.com/2867/

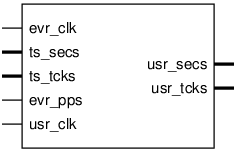

Pinout

Ports

Signal |

Direction |

Description |

|---|---|---|

evr_clk |

Input |

|

ts_secs[31:0] |

Input |

|

ts_tcks[31:0] |

Input |

|

evr_pps |

Input |

|

usr_clk |

Input |

|

usr_secs[31:0] |

Output |

|

usr_tcks[31:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in evr_ts_cdc Source File

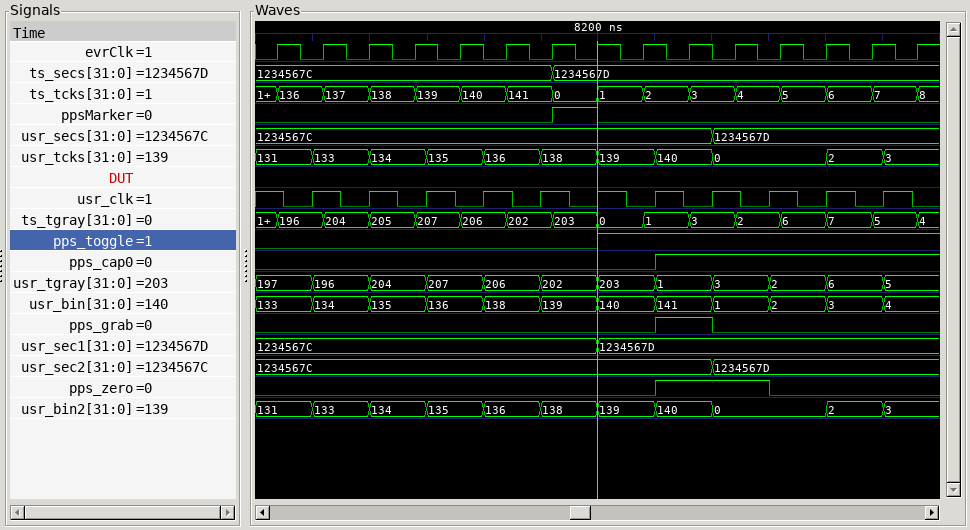

Timing Diagram

A GTKWave-generated timing diagram is shown below: