Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

multiply_accumulate

Description

TL;DR

accumulated += ((constant * signal) >>> downscale) + correction

Multiply a constant K to input signal and accumulate the result on enable.

Notice downscale, this is meant to downscale the input into the accumulator

Useful in times of high “natural” integration gain: like running with a superconducting cavity

correction comes from some externally-supplied feedforward, maybe derived from the previous pulse

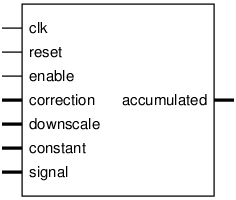

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

CW |

? |

? |

17 |

|

KW |

? |

? |

18 |

Constant Width |

SW |

? |

? |

18 |

Signal Width |

OW |

? |

? |

21 |

OutputWidth: Desired bitwidth of the accumulator |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

reset |

Input |

|

enable |

Input |

|

correction[CW-1:0] |

Input |

|

downscale[3:0] |

Input |

|

constant[KW-1:0] |

Input |

|

signal[SW-1:0] |

Input |

|

accumulated[OW-1:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in multiply_accumulate Source File

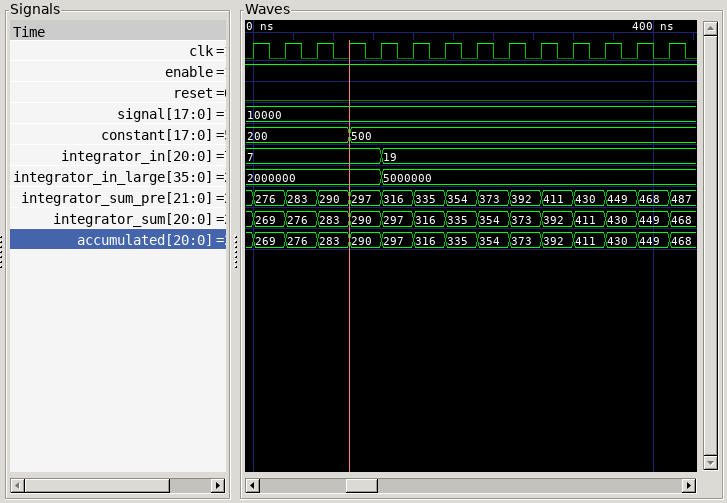

Timing Diagram

A GTKWave-generated timing diagram is shown below: