Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

complex_mul_flat

Description

TODO:

Could potentially save a cycle in the flip-flop, by combining Add and Saturate into 1 cycle

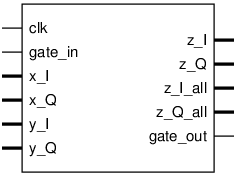

Pinout

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

Rising edge clock input; all logic is synchronous in this domain |

gate_in |

Input |

Flag marking input data valid |

x_I[17:0] |

Input |

Multiplicand 1, real |

x_Q[17:0] |

Input |

Multiplicand 1, imag |

y_I[17:0] |

Input |

Multiplicand 2, real |

y_Q[17:0] |

Input |

Multiplicand 2, imag |

z_I[17:0] |

Output |

Result, real |

z_Q[17:0] |

Output |

Result, imag |

z_I_all[35:0] |

Output |

Result, real, large |

z_Q_all[35:0] |

Output |

Result, imag, large |

gate_out |

Output |

Delayed version of gate_in |

Implementation and use

The portable Verilog implementation can be found in complex_mul_flat Source File

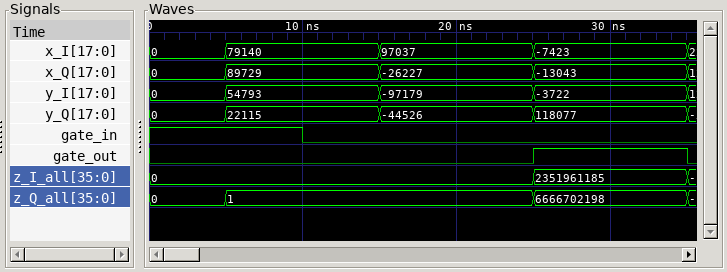

Timing Diagram

A GTKWave-generated timing diagram is shown below: