Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

phase_diff

Description

DMTD measurement of clock phasing

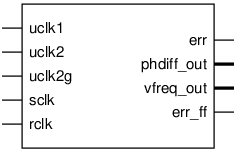

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

order1 |

? |

? |

1 |

|

order2 |

? |

? |

1 |

|

dw |

? |

? |

14 |

|

delta |

? |

? |

16 |

Ports

Signal |

Direction |

Description |

|---|---|---|

uclk1 |

Input |

unknown clock 1 |

uclk2 |

Input |

unknown clock 2 |

uclk2g |

Input |

|

sclk |

Input |

sampling clock |

rclk |

Input |

readout clock (data transfer, local bus) |

adv[dw-1:0] |

Input |

make adv a runtime variable |

err |

Output |

|

phdiff_out[dw-2:0] |

Output |

|

vfreq_out[dw-1:0] |

Output |

|

err_ff |

Output |

Implementation and use

The portable Verilog implementation can be found in phase_diff Source File

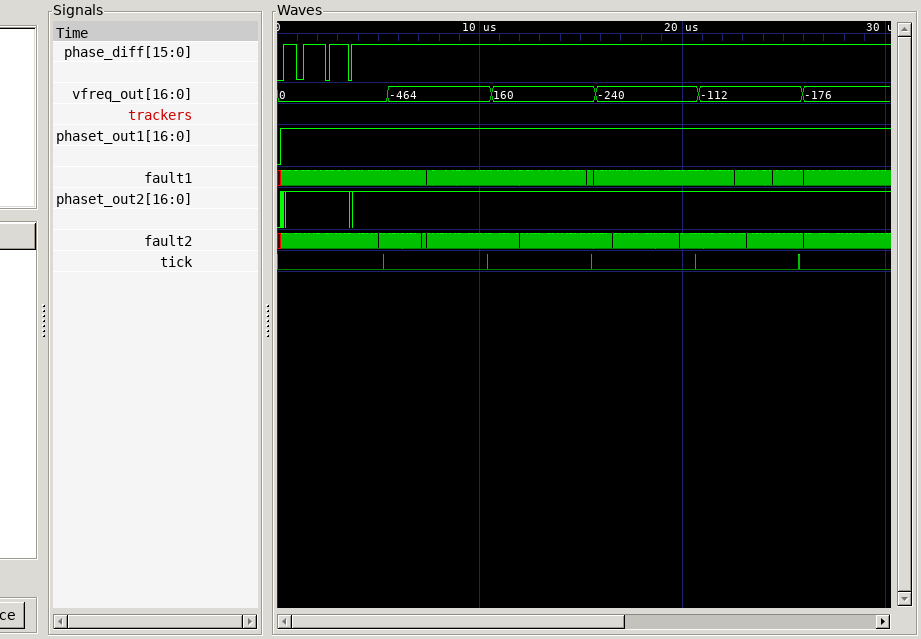

Timing Diagram

A GTKWave-generated timing diagram is shown below: