Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

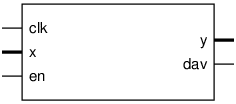

isqrt

Description

Simple-minded integer square root

Result is truncated not rounded

General purpose with the caveat that XWIDTH should be greater than 3.

(X_WIDTH+1)/2 + 1 cycles per operation, non-pipelined.

Asserting en when computation is in progress will

cancel the computation and start another.

With XWIDTH=32, synthesizable to 110 MHz on Spartan3-5.

W. Eric Norum, Lawrence Berkeley National Laboratory

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

X_WIDTH |

? |

? |

32 |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

x[X_WIDTH-1:0] |

Input |

|

en |

Input |

|

y[((X_WIDTH+1)/2)-1:0] |

Output |

|

dav |

Output |

Implementation and use

The portable Verilog implementation can be found in isqrt Source File