Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

multi_sampler

Description

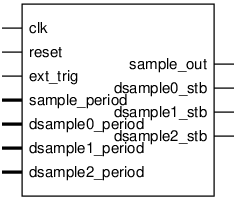

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

sample_period_wi |

? |

? |

8 |

|

dsample0_en |

? |

? |

0 |

|

dsample0_wi |

? |

? |

8 |

|

dsample1_en |

? |

? |

0 |

|

dsample1_wi |

? |

? |

8 |

|

dsample2_en |

? |

? |

0 |

|

dsample2_wi |

? |

? |

8 |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

reset |

Input |

|

ext_trig |

Input |

|

sample_period[sample_period_wi-1:0] |

Input |

|

dsample0_period[dsample0_wi-1:0] |

Input |

|

dsample1_period[dsample1_wi-1:0] |

Input |

|

dsample2_period[dsample2_wi-1:0] |

Input |

|

sample_out |

Output |

|

dsample0_stb |

Output |

|

dsample1_stb |

Output |

|

dsample2_stb |

Output |

Implementation and use

The portable Verilog implementation can be found in multi_sampler Source File

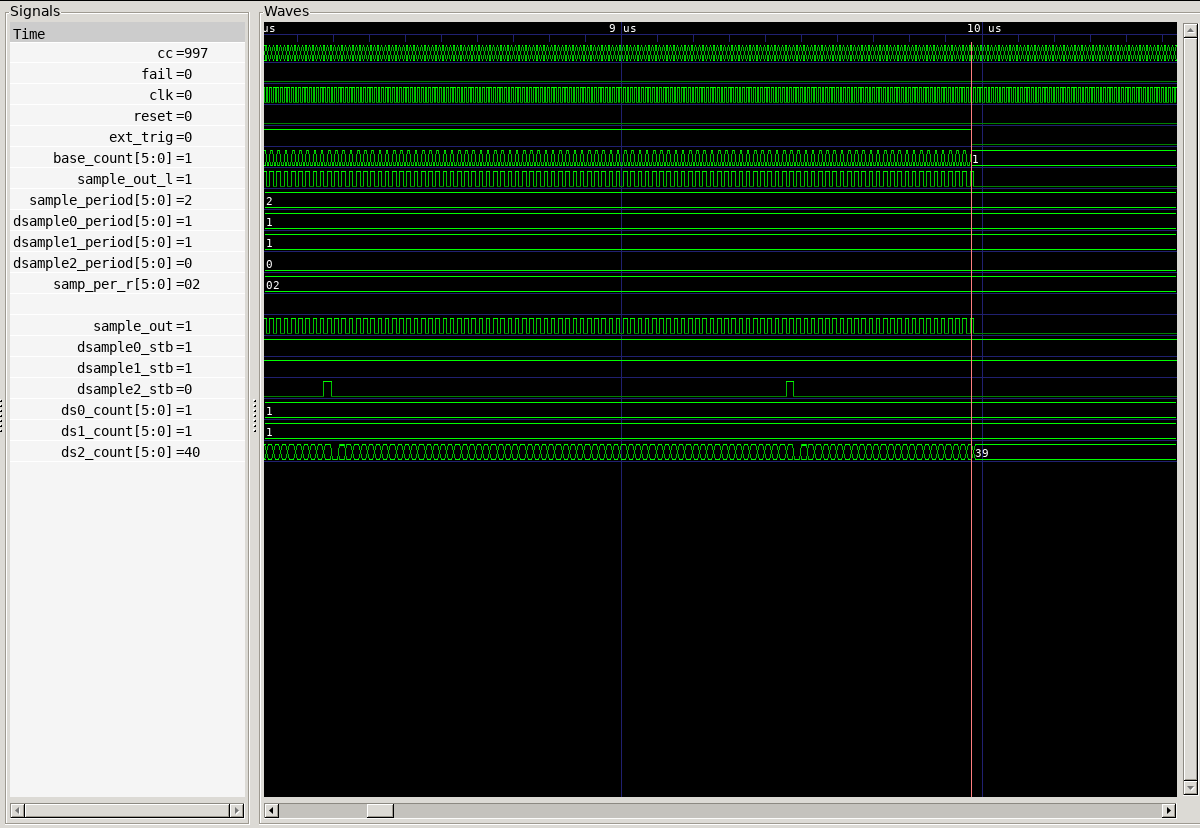

Timing Diagram

A GTKWave-generated timing diagram is shown below: