Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

cordic_mux

Description

in this module,

data flows from in_iq, through the CORDIC, to out_mp

data flows from in_xy and in_ph, through the CORDIC, to out_iq

delay is 23 clock cycles

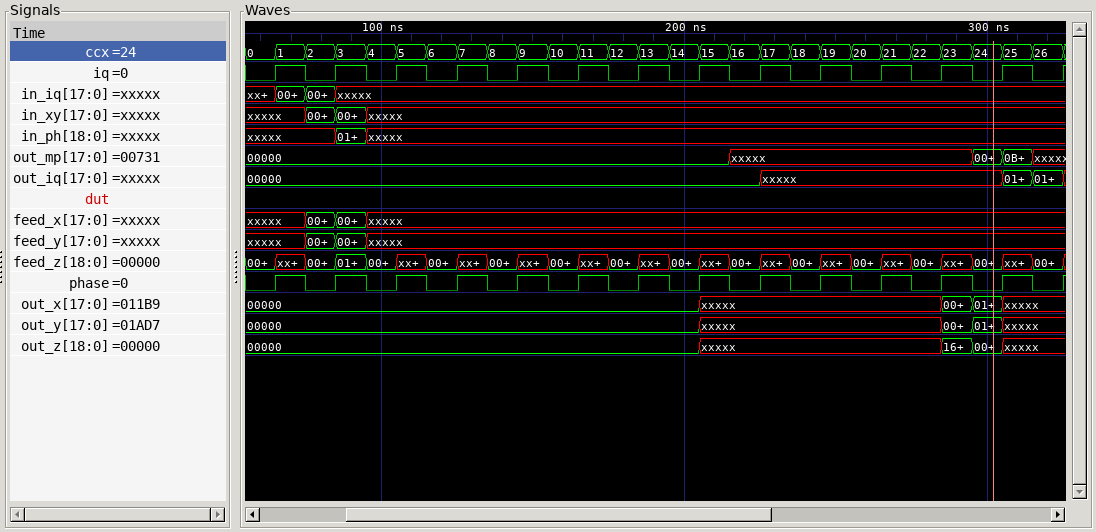

1 2 3 4 23 24 25 26 27

clk -_/-_/-_/-_/-_/-…_/-_/-_/-_/-_/-_/-

phase ___/—___/—___/-…_/—___/—___/—__

in_iq . I Q . . . . . . .

out_mp . . . . . . M P . .

in_xy . . X Y . . . . . .

in_ph . . . P . . . . . .

out_iq . . . . . . . I Q .

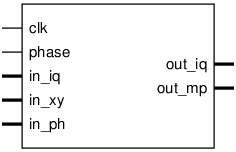

Pinout

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

phase |

Input |

|

in_iq[17:0] |

Input |

|

out_iq[17:0] |

Output |

|

in_xy[17:0] |

Input |

|

in_ph[18:0] |

Input |

|

out_mp[17:0] |

Output |

Implementation and use

The portable Verilog implementation can be found in cordic_mux Source File

Timing Diagram

A GTKWave-generated timing diagram is shown below: