Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

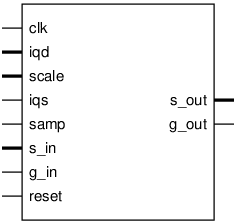

mon_2chiq

Description

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

dwi |

? |

? |

16 |

data width |

rwi |

? |

? |

28 |

result width |

davr |

? |

? |

3 |

how many guard bits to keep in output of multiplier |

dwlo |

? |

? |

18 |

Local Oscillator data width |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

timespec 8.4 ns |

iqd[dwi-1:0] |

Input |

two-way interleaved data |

scale[17:0] |

Input |

e.g., 18’d61624 = floor((32/33)^2*2^16) |

iqs |

Input |

sync high when iq_data holds I, low when iq_data holds Q |

samp |

Input |

|

s_in[rwi-1:0] |

Input |

|

s_out[rwi-1:0] |

Output |

|

g_in |

Input |

|

g_out |

Output |

|

reset |

Input |

Implementation and use

The portable Verilog implementation can be found in mon_2chiq Source File