Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

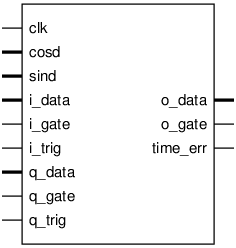

flevel_set

Description

Name: Set carrier level from I and Q

% Provide LO at cosd and sind ports

Essentially a dot product of the LO signal [cosd, sind] with [i_data, q_data]

N.B.: full-scale negative is an invalid LO value.

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

i_dw |

? |

? |

17 |

XXX don’t change this |

q_dw |

? |

? |

17 |

XXX don’t change this |

o_dw |

? |

? |

16 |

XXX don’t change this |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

|

cosd[17:0] |

Input |

LO input |

sind[17:0] |

Input |

LO input |

i_data[i_dw-1:0] |

Input |

|

i_gate |

Input |

|

i_trig |

Input |

I baseband |

q_data[q_dw-1:0] |

Input |

|

q_gate |

Input |

|

q_trig |

Input |

Q baseband |

o_data[o_dw-1:0] |

Output |

|

o_gate |

Output |

|

time_err |

Output |

Implementation and use

The portable Verilog implementation can be found in flevel_set Source File