Attention

This documentation is a work in progress. Expect to see errors and unfinished things.

rot_dds

Description

Phase Rotating Direct Digital Synthesis of sin/cos

18 bit output coming from cordicg

Note that phase_step_h and phase_step_l combined fit in a 32-bit word.

This is intentional, to allow atomic updates of the two controls

in 32-bit systems. Indeed, when modulo==0, those 32 bits can be considered

a simple fast binary DDS control for quirky (non-binary-rounding) phase

steps like:

7/33 for LCLS-II

8/11 for SSRF

9/13 for Argonne RIA

Synthesizes to ??? slices at ??? MHz in XC3Sxxx-4 using XST-??

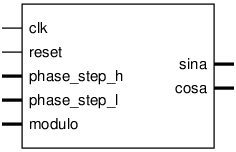

Pinout

Parameters

Name |

Min |

Max |

Default |

Description |

|---|---|---|---|---|

lo_amp |

? |

? |

18 |

Ports

Signal |

Direction |

Description |

|---|---|---|

clk |

Input |

timespec 9.0 ns |

reset |

Input |

active high, synchronous with clk |

sina[17:0] |

Output |

|

cosa[17:0] |

Output |

|

phase_step_h[19:0] |

Input |

|

phase_step_l[11:0] |

Input |

|

modulo[11:0] |

Input |

Implementation and use

The portable Verilog implementation can be found in rot_dds Source File

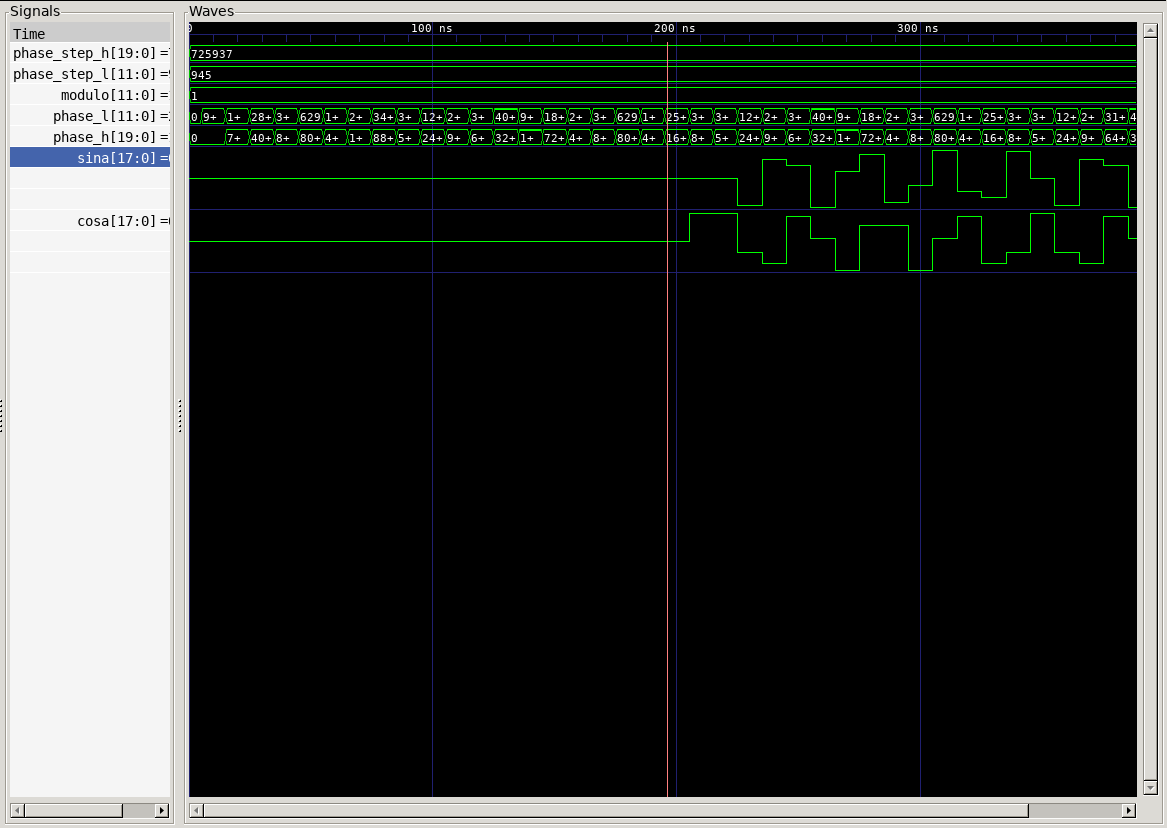

Timing Diagram

A GTKWave-generated timing diagram is shown below: